FPGA时序约束基础

一、时序约束的目的

由于实际信号在FPGA内部期间传输时,由于触发器等逻辑期间并非理想期间,因此不可避免地存在传输延时,这种延迟在高速工作频率、高逻辑级数时会造成后级触发器地建立时间和保持时间不满足,造成时序违例。(这也是为什么需要把FPGA设计不能以高级编程语言思想看的原因,设计时,需要做到“心中有电路”)一般来说在一个高速系统(时钟频率大于100M),或存在高速信号如DDR,千兆网络等情况下,必须进行时序分析和约束,以提高系统的鲁棒性和稳定性。

二、基本概念

2.1 建立时间和保持时间

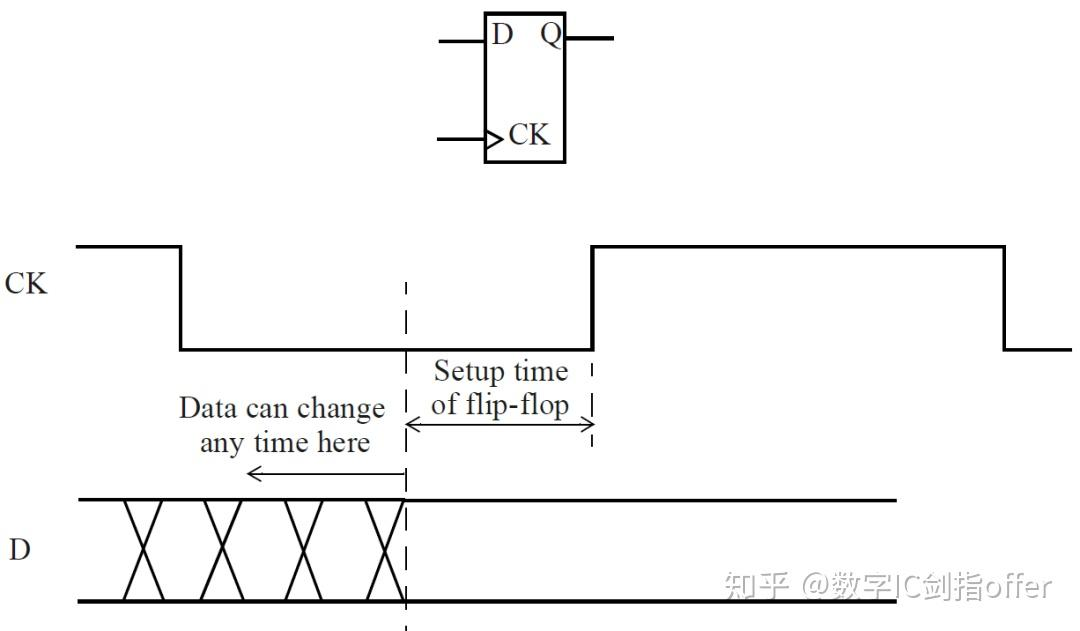

setup time是指在时钟有效沿(下图为上升沿)之前,数据输入端信号必须保持稳定的最短时间。

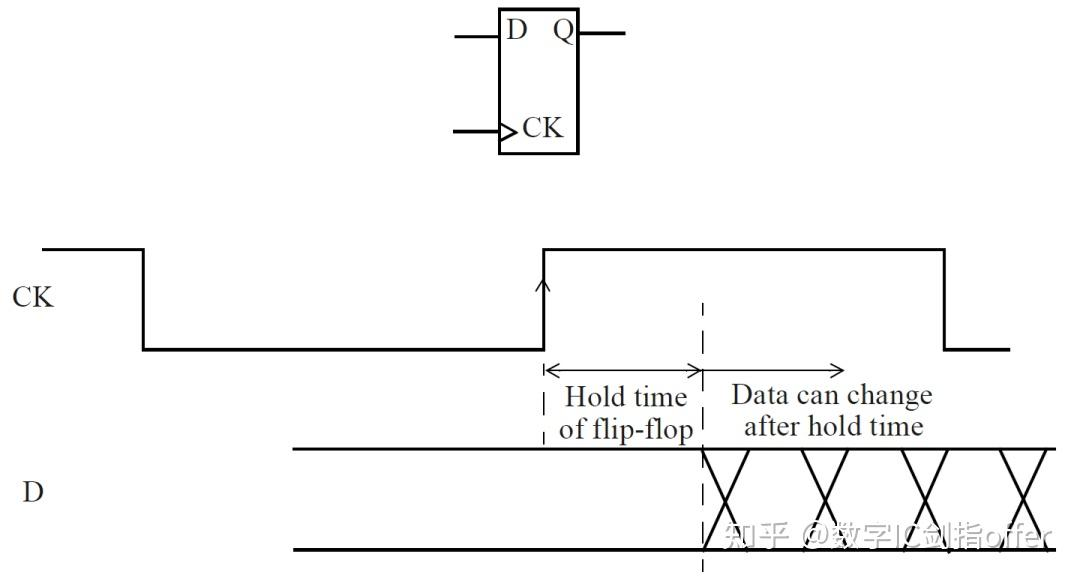

hold time是指在时钟有效沿(下图为上升沿)之后,数据输入端信号必须保持稳定的最短时间。hold time时序检查确保新数据不会在触发器稳定输出初始数据之前过早到达D端而覆盖其初始数据。

简单来说:数据传输至触发器时,数据必须在时钟的建立时间前保持稳定,而且数据必须保持到时钟的保持时间点后才能撤销,才能保证该级触发器可以正常寄存该数据。

三、模型分析

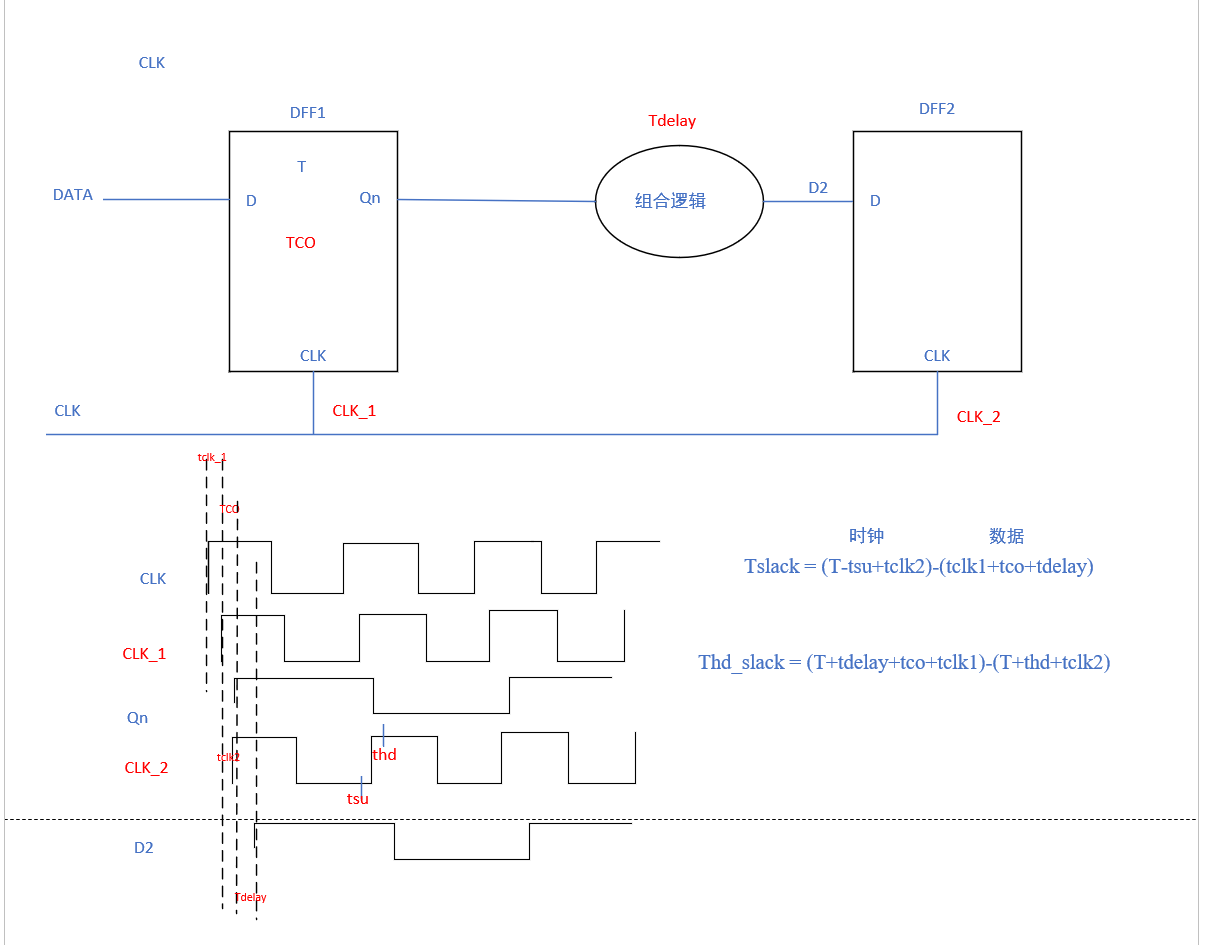

下面以经典的时序分析模型分析:

如图,data信号传输经存在DFF1、组合逻辑后传输至DFF2,由于触发器延迟tco和组合逻辑延时,clk1传输延迟,

因此建立时间余量为:

Tslack = (T-tsu+tclk2)-(tclk1+tco+tdelay),

保持时间余量为:

Thd_slack = (T+tdelay+tco+tclk1)-(T+thd+tclk2)

以上可以看出,系统的极限性能参数(时钟能跑多快,即T的大小)只与建立时间余量有关。